Addierwerke in der arithmetisch logischen Einheit (ALU)

aus der Vorlesung Rechnertechnik vom 21.03.2018

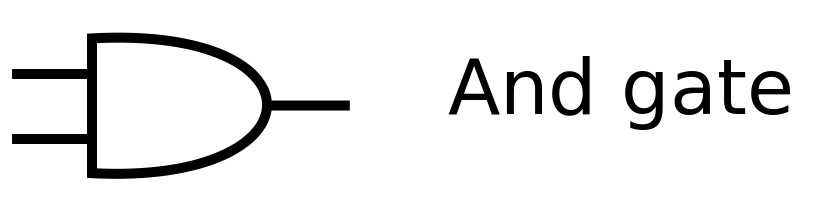

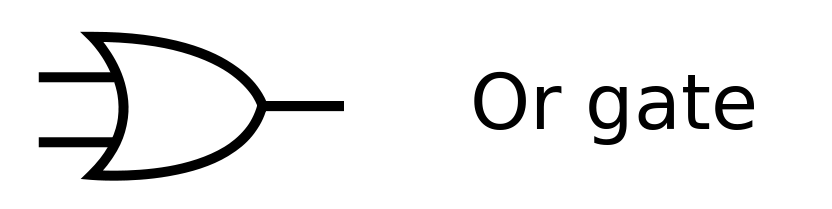

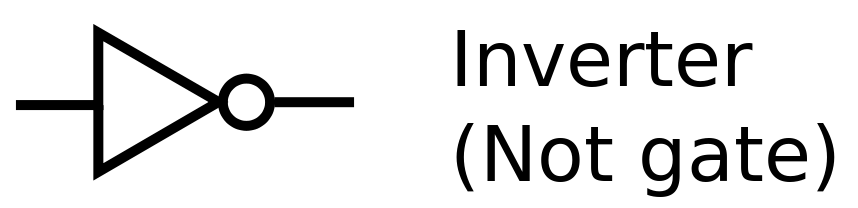

Mit den Schaltsymbolen

-

AND

Abbildung 1:AND-Gatter -

OR

Abbildung 2:OR-Gatter -

NOT

Abbildung 3:NOT-Gatter

ergibt sich folgende Schaltung:

Abbildung 4: Halbaddiererschaltung

Konstruktion der arithmetischen logischen Einheit (ALU)

Die arithmetisch logische Einheit besteht in der Regel aus Hardware zur Berechnung der vier Grundrechenarten und Logik-Hardware zur bitweisen Verknüpfung von Operanden.

Die Arithmetik der Gleitpunktzahlen ist auf die Arithmetik der Festpunktzahlen zurückführbar; z.B. indem die Exponenten so angepasst werden, dass die Mantissen ganzzahlig werden.

Es verwundert zunächst, dass mit einem Rechner, der nur Hardware für die Grundrechenarten besitzt, auch komplizierte Funktionen wie z.B. Sinus, Cosinus oder Logarithmen berechnet werden können. Solche Funktionen werden mit Hilfe von numerischen Verfahren wie z.B. Potenzreihenentwicklungen oder Tschebyscheff-Approximationen auf die Grundrechenarten zurückgeführt und die Algorithmen in Software-Bibliotheken hinterlegt.

Addierwerke (Subtrahierwerke)

Die Addition von Dualzahlen verläuft analog der Addition der Dezimalzahlen mit Bildung eines Übertrags (Carry, ) und eines Restes ().

Für die erste Stelle wird ein Schaltnetz mit den Eingängen und sowie den Ausgängen und konstruiert.

Die entsprechende Wahrheitstabelle sieht wie folgt aus:

also und .

Das zugehörige Schaltnetz ist ein Halbaddierer.

Abbildung 5: Schaltbild eines Halbaddierers

Für die zweite und folgenden Stellen konstruiere man ein Schaltnetz mit den Eingängen , und sowie den Ausgängen und .

Wahrheitstabelle für einen Volladdierer

Entsprechendes Schaltnetz

Abbildung 6: Schaltnetz eines Volladdierers

Um aus Halb- und Volladdierern ein Addierwerk aufzubauen, müssen die Summanden und die Summe in Registern gespeichert werden. Register sind aus 1-Bit Speicher, sogenannte Flip-Flops, aufgebaut. Das einfachste Flip-Flop ist das RS-Flip-Flop mit einem Set-Eingang (S) und einem Reset-Eingang (R).

Wahrheitstabelle für ein RS-Flip-Flop

| stabile Speicherfunktion | ||||

set |

||||

reset |

||||

| unzulässige Eingänge |

Entsprechende Schaltung

Abbildung 7: Schaltung für einen RS-Flip-Flop

Nun sollen Flip-Flops nicht zu jeder Zeit set- oder reset-Signale bearbeiten, sondern nur zu fest definierten Zeitpunkten. Zum Beispiel wird ein Operand, der auf den Leitungen des Datenbusses anliegt, zu einem bestimmten Zeitpunkt in ein Register übernommen.

Die Zeitpunkte, zu denen set- oder reset-Signalen bearbeitet werden, werden durch einen Taktgeber (Clock) bestimmt, welcher ein Taktsignal generiert.

Um set- und reset-Signale wirksam werden zu lassen, wenn das Taktsignal den Wert hat, wird die Schaltung des RS-Flip-Flops wie folgt erweitert:

Sei ein allgemeines (Daten-)

Signal:

Abbildung 8: Schaltnetz eines D-Flip-Flops

anschaulich: Beispiel für den Signalverlauf von Clock, Flip-Flop-Eingang und Flip-Flop-Ausgang :

Abbildung 9: Signalverlauf an einem D-Flip-Flop

Es kann nun ein Addierwerk aus Halb- und Volladdierern und zwei Registern aufgebaut werden.

Dieses Addierwerk arbeitet wie folgt: Zunächst werden die beiden Summanden in die Register und geladen. Für die Berechnung der lokalen Überträge bis vergeht in jedem Addierer einer einzelnen Bit-Stelle eine gewisse Verzögerungszeit .

Die Summe der beiden Summanden steht erst nach der Zeit stabil an den Ausgängen bis

an, da im pessimistischen Fall ein Übertrag durch alle Addierer hindurchgereicht werden muss. Da das Ergebnis nach einer Taktzeit von den Ausgängen bis in ein Register geladen wird, gilt für die Dauer eines Taktes

da so groß sein muss, dass alle Verknüpfungen sicher durchgeführt werden. Die Additionszeit dieses Addierwerks ist somit unabhängig davon, wieviele Bitstellen der Summanden mit belegt sind. Die Addition dauert für Zahlen der Länge genau so lang wie für Zahlen der Länge .

Der von-Neumann-Addierer

Der von-Neumann-Additionsalgorithmus führt zu einem schnelleren Addierwerk, bei dem im Mittel weniger Durchschaltzeiten notwendig sind.

Der Algorithmus läuft wie folgt ab:

- Lade Summanden in - und -Register.

- Bilde komponentenweise die Summe aus und (Bitstellen ) und speichere das Ergebnis in .

Bilde komponentenweise die Überträge aus und und speichere diese in . - Ist irgendeine Bitstelle im Register ungleich 0 (), so fahre bei Punkt 2. fort.

Sind alle gleich 0, so terminiert der Algorithmus und die Summe steht im -Register.

Beispiel:

| 0. Durchlauf | ||

| 1. Durchlauf | ||

| 2. Durchlauf | ||

| 3. Durchlauf | ||

Fertig, weil alle .

Abschätzung der Additionszeit beim von-Neumann-Addierer

Im schlechtesten Fall sind zur Addition von zwei -stelligen Dualzahlen Durchläufe des Algorithmus erforderlich, da ein Übertrag mit jedem Durchlauf um mindestens eine Stelle im -Register “nach links” wandert und rechts eine nachgezogen wird.

⚠️ Die mittlere Anzahl an Durchläufen ist jedoch wesentlich geringer. ⚠️

Dazu folgende Überlegung:

Zu Beginn der Addition sind im -

und -Register

im Mittel Bitstellen mit belegt.

Betrachte dazu :

Anzahl möglicher Eingangszustände:

Gesamtzahl der Einsen:

Anzahl möglicher Zahlen:

somit: mittlere Anzahl der Einsen pro Zahl ist: .

bei mögliche Zahlen

Gesamtzahl der Einsen:

mittlere Anzahl der Einsen pro Zahl:

günstigster Fall:

weniger günstiger Fall:

schlechtester Fall:

Aus den Tabellen erkennt man, dass sich die Anzahl der mit belegten Bitstellen im -Register bei jedem Durchlauf im Mittel halbiert.

Frage: Wieviele Durchläufe werden bei -stelligen Dualzahlen im Mittel benötigt?